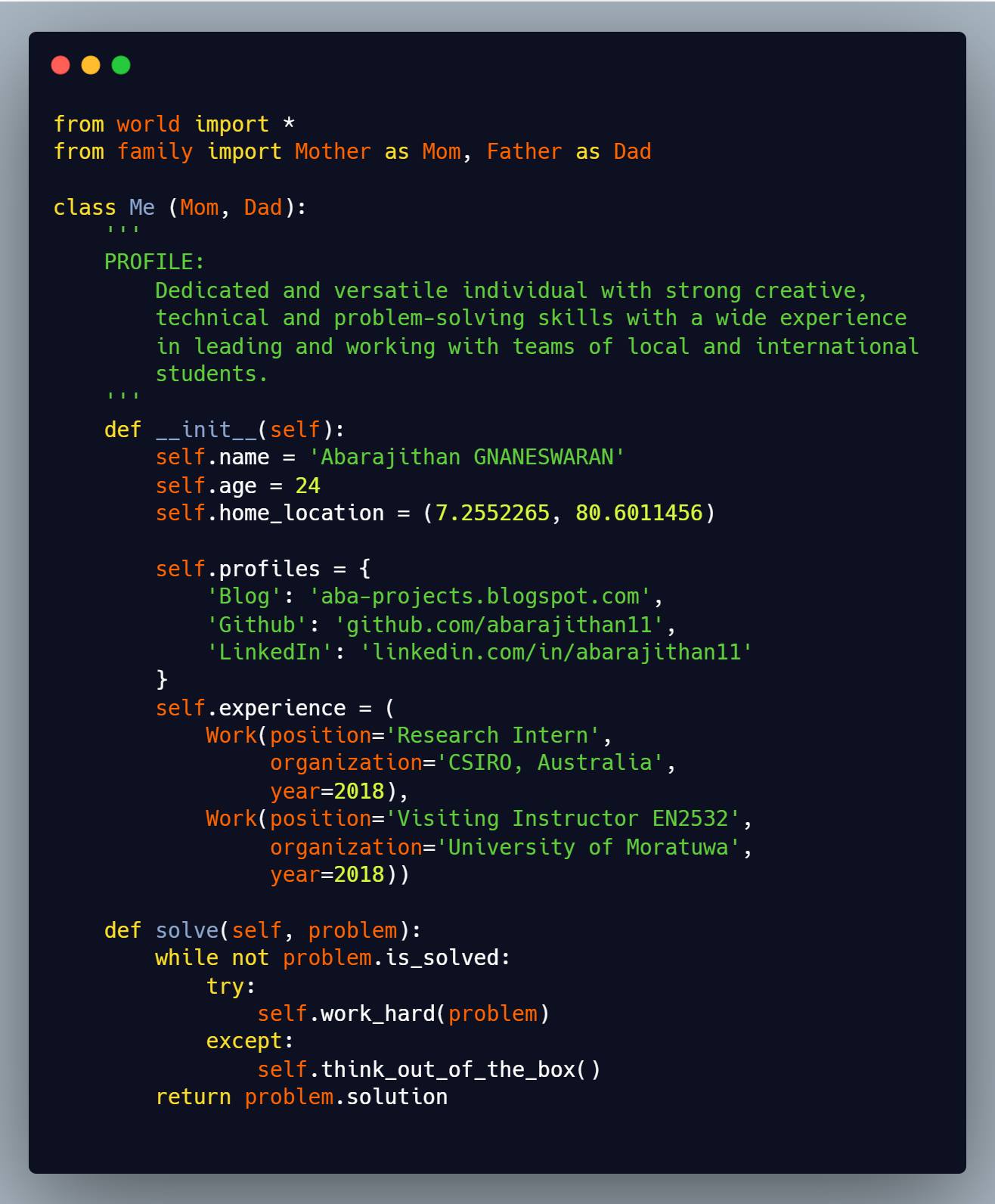

G Abarajithan

PhD candidate (CE) building parameterized RTL subsystems (AXI SoCs, DMA control, accelerators) and end-toend SoC integration (FPGA+ASIC flows). Current work develops Hyperflow-guided hardware security fuzzing with information-flow tracking to expose vulnerabilities in Out-of-Order CPUs and SoC fabrics.