G Abarajithan

PhD candidate (CE) building parameterized RTL subsystems (AXI SoCs, DMA control, accelerators) and end-toend SoC integration (FPGA+ASIC flows). Current work develops Hyperflow-guided hardware security fuzzing with information-flow tracking to expose vulnerabilities in Out-of-Order CPUs and SoC fabrics.

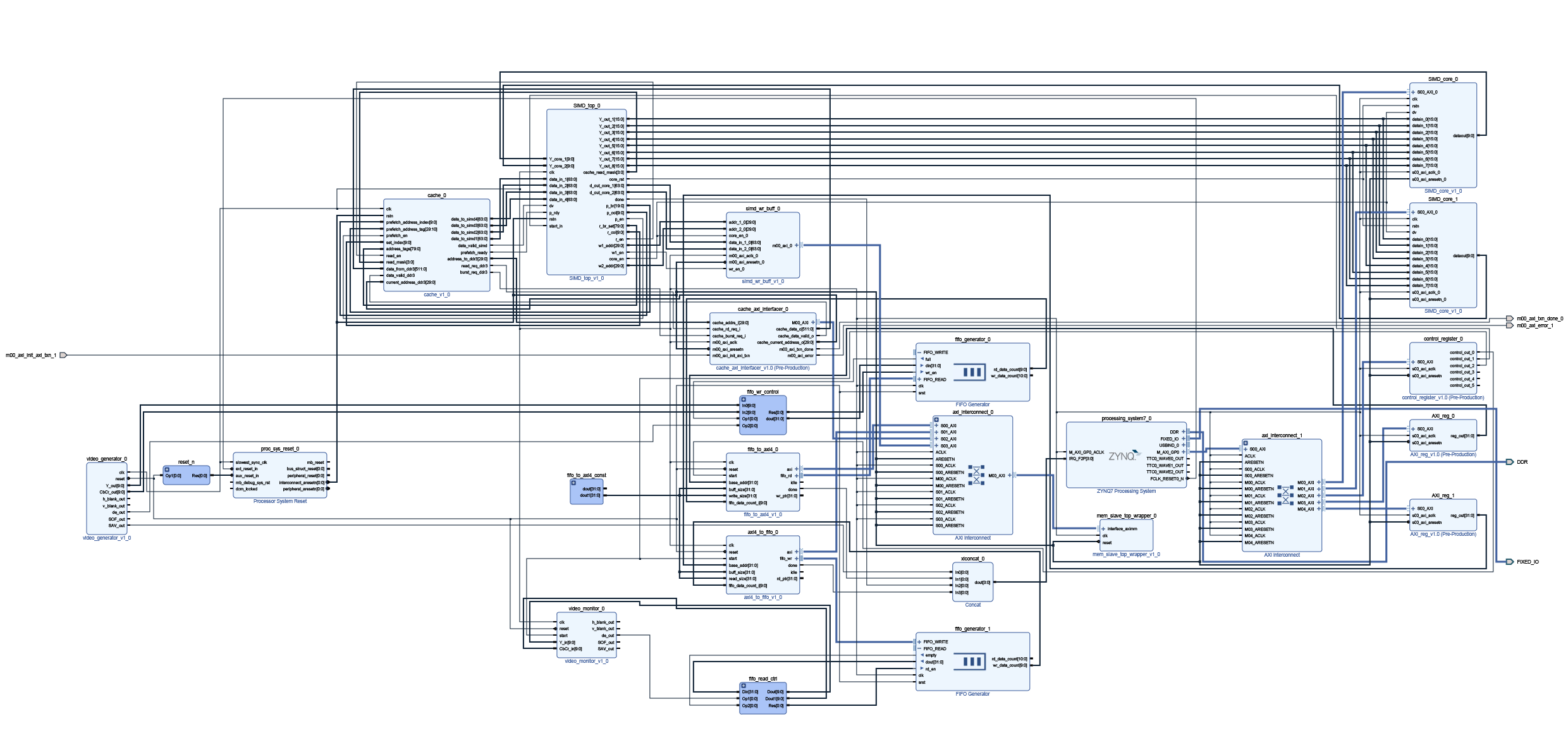

![Neural Chip Design [4/4: SoC Integration & Firmware]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2022/01/sys-4.jpg)

![Neural Chip Design [3/4: RTL Design & Verification]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2022/01/vlcsnap-2022-01-30-00h01m19s402.png)

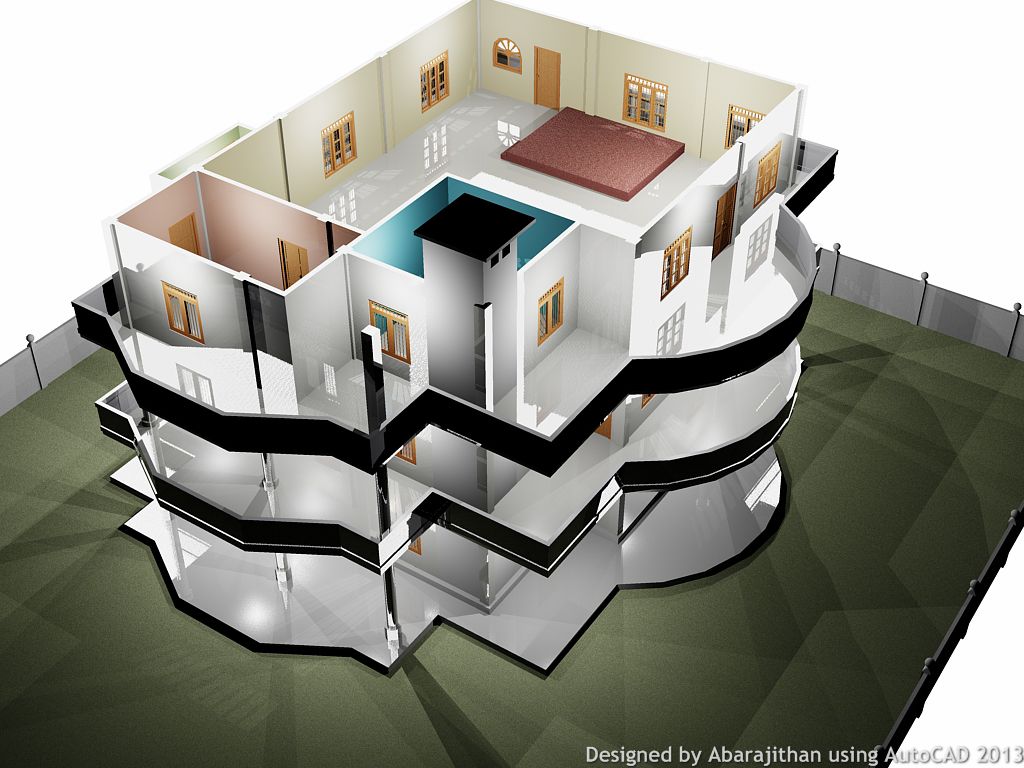

![Neural Chip Design [2/4: Golden Model]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2022/01/b6f87d_cec29645262b492f95a30c10edec1090_mv2.jpg)

![Neural Chip Design [1/4: Overview]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2022/01/cov-14.jpg)

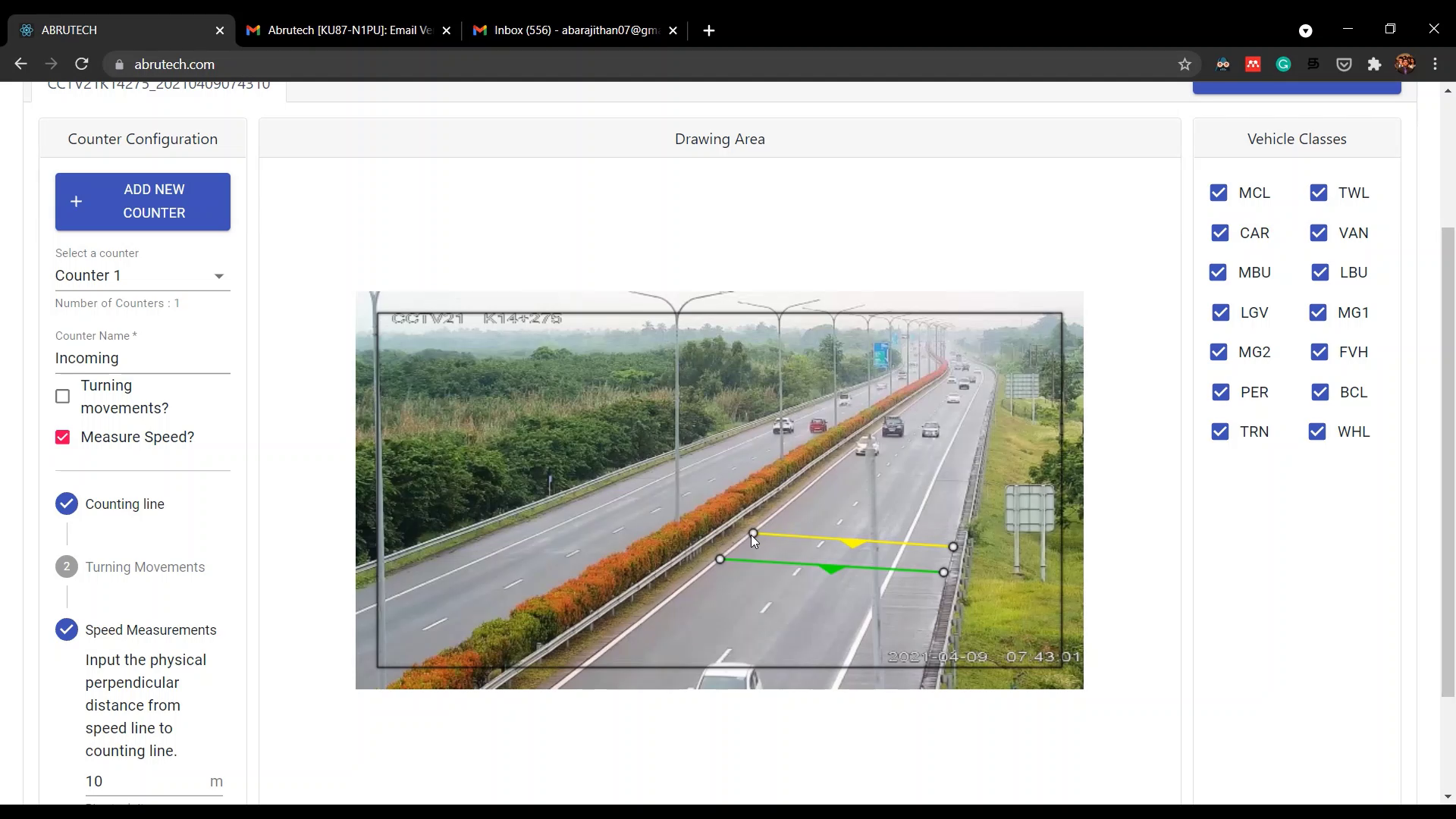

![Vision-Based Adaptive Traffic Control on an MPSoC [ARM+FPGA]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2021/11/IMG_20191204_112837--1--1.jpg)

![My Paper-Writing Workflow [Inkscape, Python, Mendeley, VSCode, Git]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2021/11/53-3.png)

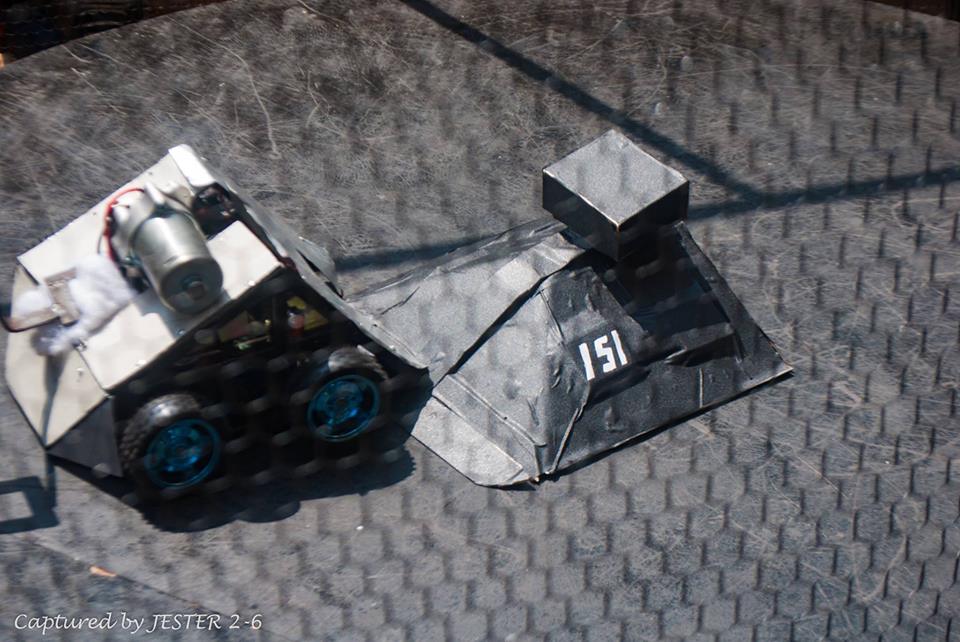

![Gollum - Ring Finding Robot: [GPS, obstacle avoiding, wall following, color detection, parallel alignment]](https://pub-0718e0124bee4fb880ecad10710509d5.r2.dev/content/images/2021/11/20170719_115907.jpg)