Webinars: Design and Simulation with SystemVerilog

In 2020 November, I conducted a free, open, and independent hands-on webinar.

- It was widely successful, with 170+ attending from 9 institutes in Sri Lanka, India, and Sweden.

- Zoom recording was downloaded over 2300 times.

- Feedback about the content, visuals, and teaching style was overwhelmingly positive. I'm so happy about this 😄.

Why?

During my undergrad years, I found that several students find digital design counterintuitive. They approach HDLs with the software programming mindset. In addition, our program does not teach an HDL explicitly but expects students to pick up from Verilog basics and learn as they go. As a result, many are unaware of the advanced features of SystemVerilog that make their lives easy by reducing bugs and saving time.

During my undergraduate project, I used SystemVerilog for features such as multidimensional ports. When I was stranded in Delhi due to unexpected COVID lockdowns during my solo backpacking, I started reading technical books of Stuart Sutherland and Chris Spear on the language and took notes. When I returned, I rebuilt Kraken using the advanced features I had learned.

I wanted to pass this knowledge on to the students. So, I picked this as the first topic of my initiative: Missing Semester, inspired by MIT's namesake.

My Teaching Method

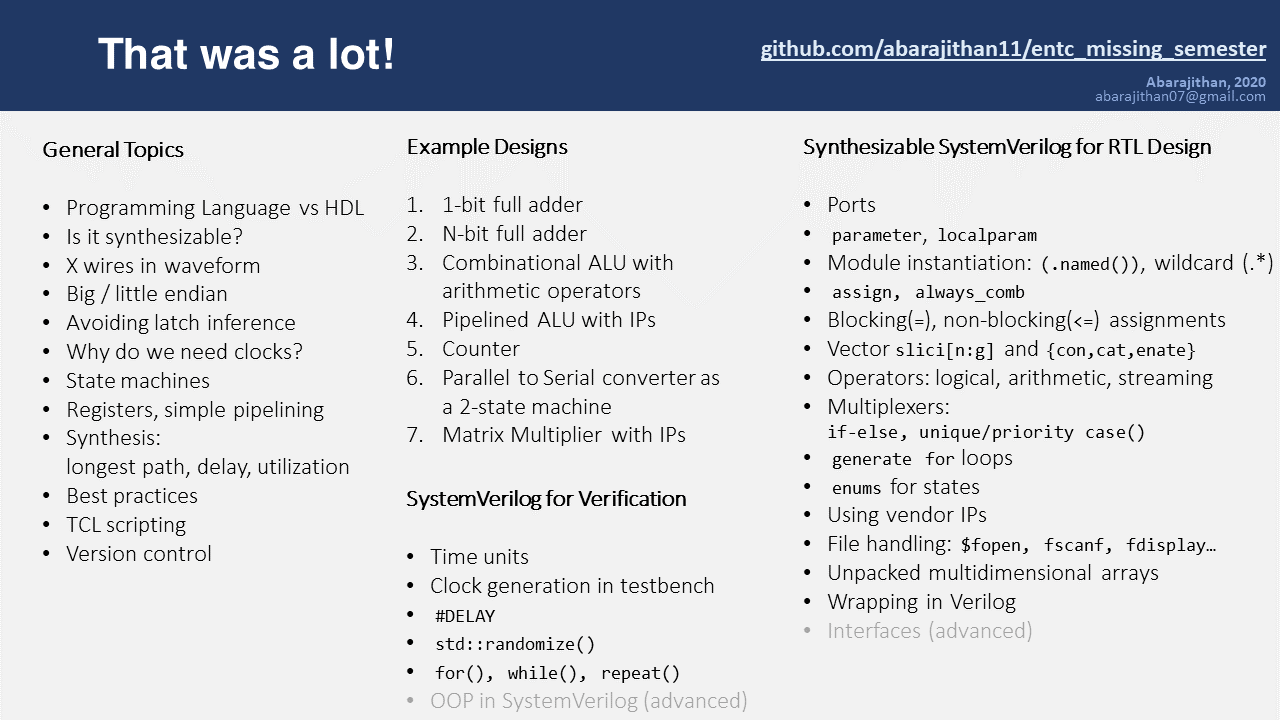

I built the course as a set of 7 example circuits, with increasing complexity. For each circuit, I explained the background, the problem, how it is designed, then implementation and verification. I put a lot of effort into slide aesthetics and animations, to aid their understanding.

All Slides [download]

Feedback [all]

I am a graduate of Kristianstad University in Sweden and currently, I am working at Forbytes. Thank you so much for sharing those details with me. I loved your first and second sessions. But couldn't join for the third one due to my busy schedule. I enjoyed the session on system verilog you conducted today very much. Is it possible to share a list containing the books and videos I can read and watch to learn system verilog from the scratch? Thank you for the session again. It was pretty awesome and interesting.

What I feel is that this session was the cream of the HDL extracted from internet and every references. If you can do this kind of dedications, it would really helpful for the new comers to the field. Thank you vary much aiya and all the best for your future works! <3

This was very good. I had almost 0 experience in this, just the semester 3 practical. As a beginner I leant a lot. Thank you very much. The speed was alright, almost nothing to complain about. Thank you once again.

I loved the session. It was amazing how the session covered a lot of content within such a short period of time while concentrating on the basics as well. Thank you for such a helpful session. In the session, the presenter asked us to write code before explaining the code. It will be better if the code was explained a bit before at least what the code does in chunks and asked us to write the code, it will be better. I would like to know proper resources where we can refer with respect to SystemVerilog, so that whenever we have a knowledge gap we will know where to refer to.

The session was excellent. I have done digital circuit designs using Verilog before. But, I did not have a clear understanding on most of the stuff. Today, I could understand many of them with your step by step explanations. Thanks a lot for that. The method of delivery was fine to me. Definitely I will join for the next sessions as well. Thank you again for conducting such a fruitful session.

I'm an NDES diploma holder from IET Katunayaka. This field is only heard by me during our training sessions and never been taught to us during our academic sessions. This lecture series is very valuable for us and thank you very much for open knowledge sharing and providing recorded zoom videos. Your teaching style is very attractive and not boring. I wish you all the best and hope you will continue to share your valuable knowledge with the local technologically curious audience. Please make sure to give more publicity to theses sessions since I got the email only from a good friend of mine.

excellent session. nice visuals. clear explanations. speed was adequate so that students can grasp the idea. looking forward for advanced stuff. thank you

session 4 was very interesting with the matrix multiplication part. It would be very useful if you can add more applications if possible. Thank you for your time for doing all these useful sessions and hope to see more of these in future.

Sessions series was really helpful and I think, it made it easy to go deeper into the system Verilog HDL since now we know what are the limitations and capabilities of the language. It would be better if the speaker can go more slowly. As it is really difficult to move between zoom and the application software when he is explaining things. Giving some time after explanation to make things clear will be better and more productive.

Nothing big to complain. Never felt other sessions like these, this much interactive and useful. Thank you for all your effort

3rd session also was very much informative and anyone with a basic knowledge could follow. It was bit fast but was manageable as I have some prior experience with verilog coding. You covered a big area with that limited time and keep it going for more sessions in the future for other key topics as well. Thanks

The Session was okay, some of them were very advance, but it is interesting to learn. Thank you for doing this.

Thank you very much sir once again. I learnt a lot today and could get the answers for many problems that I had up to now. Thanks once again...!!!

The session was comprehensive and clear. Within the time constraint, a better insight to the subject is provided. Thank you for your hard work.

Thank you very much sir. This is extremely helpful for me. I have met some of these issues that you spoke about today and didn't know how to overcome those ones and now I understand how to solve those problems. Thank you very much once again...!!!

fruitful session. nice visuals. thank you so much. My suggestion is it is better to have the final project in a separate session. I guess there will be a lot to cover. this is the adequate speed to maintain. definitely, we may not be able to cover the last 3 in 2 hours. thank you

good explanation and you answered our questions clearly. appreciate it

Very much informative, clear and interactive. Appreciate your sharp and broad knowledge on the subject

Hopeful for more sessions like this in future too

Thank you for conducting this session. It was really helpful in understanding the basics of digital designs.

The session was really really good. This makes to get into academic projects very easy. The pace of the session was also good. I would like to know more about vivado and systemverilog that will help me to do advanced projects. Hope you cover much much more in coming sessions. If possible it would be great to cover industrial aspects as well while designing and implementing.

one kindly request sir....only if you can, keep the sessions like this further with the whole ENTC junior staff, because these are very useful

Good work Anna... Our department can use this quarantine time to this kind of activities. ENTC can support more for this kind of tutorials. For a geek like me , It is very helpful. I have to spend a lot of time in finding good tutorials. Don't stop with 3 sessions. Expecting more Anna.

Nice interaction. Helped me to recall what I leaned in digital IC designing.

Well done mlli!!! Superb! nd thnx a lot for ur generous service!You had worked hard on it! You must be full contented abt ur effort mlli!!!it was truly amazing

Code

github.com/abarajithan11/entc_missing_semester/tree/master/systemverilog

Video Recordings

First video was downloaded 2279 times (and counting)

Download: dms.uom.lk/s/VMVBDESqhc7ByZv

References

- RTL Modeling with SystemVerilog for Simulation and Synthesis: Using SystemVerilog for ASIC and FPGA Design by Stuart Sutherland

Primary reference material I used for the slides. Especially for synthesizable RTL design features of SystemVerilog

- SystemVerilog for Verification: A Guide to Learning the Testbench Language Features by Chris Spear

I referred to this to understand the simulation features (OOP, assertions) of SystemVerilog

- Zynq Training by Mohammad S. Sadri [YouTube playlist]

Excellent guide on AXI4 protocol and SoC design with Vivado. Play at 1.25x speed

- Parallel Programming for FPGAs by Ryan Kastner [free download]

Notes from UCSD (University of California San Diego) on parallelizing algorithms and implementing them with Vivado HLS (C-based HDL). I'm reading this now

- Computer Organization and Design:

The Hardware/Software Interface, RISC-V Edition by David A Patterson

One of the most popular books. Especially on processor design. I haven't read it yet.